基于FPGA的RFID閱讀器設計

作者:張捍東 張淳

來源:RFID世界網

日期:2009-07-14 10:29:38

摘要:作為一項具有廣泛應用前景的技術,RFID閱讀器近年來已在多個領域發揮了重要作用。由于單片機的開發周期長且批量小,因此,采用FPGA為核心來設計高頻、遠距離的閱讀器。經驗證,它能夠快速、準確地實現曼徹斯特編碼的譯碼并進行CRC校驗。設計的通用異步收發器實現了數據的接收和發送,具有電路形式簡單、移植方便等優點。

0 引言

RFID(radio frequency identification)即射頻識別技術,是自動識別技術的一種,主要由閱讀器和電子標簽兩部分組成。通過無線射頻方式進行非接觸雙向數據通信,對目標加以識別并獲取相關數據。

閱讀器的設計是RFID系統設計中的關鍵部分,關于它的設計方案有很多種。FPGA是大規模可編程器件中的另一大類PLD(programmable logic device)器件,既繼承了ASIC的大規模、高集成度、高可靠性的優點,又克服了普通ASIC設計周期長、投資大、靈活性差的缺點,逐步成為復雜數字硬件電路設計的首選。因此,本文設計了一種基于FPGA的高頻、遠距離RFID閱讀器。

1 系統功能概述

ISO/IEC 18000-6是ISO/IEC 18000標準的一部分,它定義了工作在高頻率范圍內(860~960 MHz)射頻識別系統的空氣接口和通信協議Ⅲ,并規定了Type A和Type B兩類非接觸式射頻卡,如表1所示。

表1 兩類射頻卡的比較

閱讀器的工作原理是:標簽接收到閱讀器的響應幀后,將NRZ碼編碼成Manchester碼,并調制上載波后發送出去,閱讀器的高頻接口將該信息解調,即將載波信號濾除后,輸出Manchester碼到譯碼模塊;譯碼模塊將譯碼得到的NRZ碼串行輸出到通用異步收發器UART的接收模塊;接收模塊將其轉化為并行數據,送人并行CRC(cyclic redundancy check)模塊,UART發送模塊等待數據幀發送命令XMIT_CMD,當CRC模塊檢查到接收的數據正確,便將XMIT_CMD置為“1” ,發送模塊開始發送數據。

2 閱讀器設計方案

對目標芯片EP1 C6Q240C8,采用Quartus II開發軟件,使用VHDL語言完成對閱讀器各模塊的描述,并且調用第三方仿真工具ModelSim來進行時序仿真。Quartus II是Ahera公司的綜合性PLD開發軟件,支持原理圖、VHDL、Verilog—HDL等多種設計輸入形式,內嵌自有的綜合器以及仿真器,還可以調用第三方仿真工具完成從設計輸人到硬件配置的完整PLD設計流程。Quaaus II的設計步驟為設計輸入、設計編譯、功能仿真、時序仿真、硬件配置。

2.1 譯碼模塊

從電子標簽到閱讀器的數據傳輸可采用Manehester編碼,這將有利于發現傳輸中的錯誤。因為在比特長度內,“沒有變化”的狀態是不允許的。當多個標簽同時發送的數據位有不同值時,接收的上升沿和下降沿互相抵消,由于該狀態是不允許的,所以閱讀器利用該錯誤就可以判定碰撞發生的具體位置。在曼徹斯特編碼中,某比特位的值是由該比特長度內半個比特周期時的電平的變化(上升/下降)來表示的,從“1”跳變到“0”表示二進制“1”,從“0”跳變到“1”表示二進制“0”。

閱讀器的工作頻率為915 MHz,Manchester碼的傳送頻率為915 MHz/16。其基本設計原理是采用915 MHz作為基準時鐘clk ,利用分頻器得到基準時鐘的16分頻(clk/16)和8分頻(clk/8)。用2個D觸發器構成移位寄存器,輸人時鐘為(clk/8),將輸入的Manchester碼并行移出,并行移出的2個值為q1和q0。再構造一個比較器,采用clk/16作為輸入時鐘,這樣就能將Manchester碼在一個比特長度內的兩個電平值進行比較,如果q0=“1”,q1 =“0”,就輸出二進制“1”;如果qo=“0”,q1=“1”,就輸出二進制“0”。這樣就實現了Manchester碼的譯碼。

采用QuartusⅡ開發軟件,可以觀察到設計的RTL視圖,如圖3所示。其中mdi為輸入的Manchester碼,Out。為輸出的譯碼。

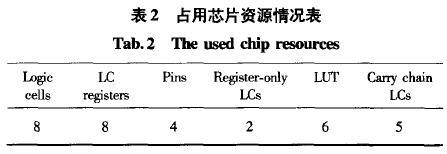

表2 占用芯片資源情況表

1001”;Out1為得到的八位二進制譯碼“11011010”。輸出的譯碼比輸入的Manchester碼延時一個周期。譯出八位二進制碼的時間僅為156.264 ns。因此,本設計能達到快速準確譯碼的目的,且占用資源少。

2.2 通用異步收發器接收模塊

接收器模塊接收譯碼模塊輸出的串行二進制碼。

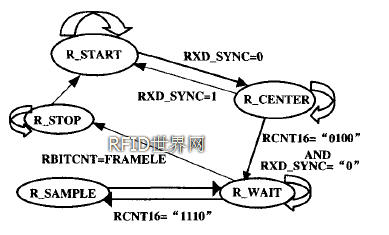

并將其轉化為并行數據輸出。接收狀態機共有R_START(等待起始位)、R_CENTER(求中點)、R_WAIT(等待采樣)、R_SAMPLE(采樣)和R_STOP(停止)這5個狀態,如圖5所示。

2.3 并行CRC模塊

通常,CRC采用線性反饋移位寄存器的串行實現,本文采用一種并行CRC運算方法。CRC校驗碼采用多項式:x16 + x12 + x5 +1。使用16個移位寄存器,每次輸入8 bits數據,相當于一次并行運算就得到了串行移位運算時需要8次移位得到的結果,具有更高的處理速度,縮短了閱讀器對卡的響應時間。

2.4 通用異步收發器發送模塊

當發送模塊處于X_START狀態時,發送一個位時間寬度的邏輯0至輸出TXD ,緊接著狀態機轉入X_WAIT狀態。XCNT16是balk的計數器。X_WAIT狀態和接收狀態機中的R_WAIT狀態相似。計數器記到15時,轉入X_SHIFT狀態,實現待發數據的并串轉換,轉換完成回到X_WAIT狀態。當數據幀發送完畢,狀態機進入X_STOP狀態,等待另一個數據幀的發送命令。

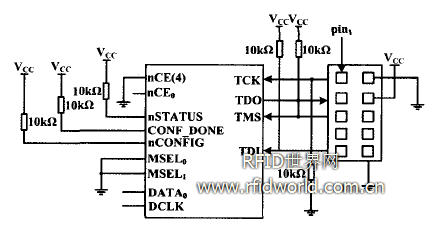

3 下載配置

EP1C6Q240C8芯片支持被動串行和JTAG兩種下載模式 ,這里采用JTAG模式對芯片進行配置。下載電纜與電路板相連的是10針插座,采用1O個小方格來表示,配置電路如圖6所示(其中nCE0懸空,DA-TA。和DCLK使用高電平或低電平驅動)。

FPGA是簡化SoC設計的一種新選擇,省略了單片機的許多附件部分。本文實現了基于ISO/IEC18000-6標準閱讀器的解碼、處理和發送功能。通過實驗證明,本設計具有解碼速度快、接收數據準確、識別率高等優點。

RFID(radio frequency identification)即射頻識別技術,是自動識別技術的一種,主要由閱讀器和電子標簽兩部分組成。通過無線射頻方式進行非接觸雙向數據通信,對目標加以識別并獲取相關數據。

閱讀器的設計是RFID系統設計中的關鍵部分,關于它的設計方案有很多種。FPGA是大規模可編程器件中的另一大類PLD(programmable logic device)器件,既繼承了ASIC的大規模、高集成度、高可靠性的優點,又克服了普通ASIC設計周期長、投資大、靈活性差的缺點,逐步成為復雜數字硬件電路設計的首選。因此,本文設計了一種基于FPGA的高頻、遠距離RFID閱讀器。

1 系統功能概述

ISO/IEC 18000-6是ISO/IEC 18000標準的一部分,它定義了工作在高頻率范圍內(860~960 MHz)射頻識別系統的空氣接口和通信協議Ⅲ,并規定了Type A和Type B兩類非接觸式射頻卡,如表1所示。

表1 兩類射頻卡的比較

Tab.1 Comparison of 2 types of radio frequency m odules

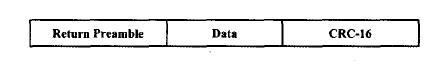

圖1 標簽響應幀格式

Fig.1 Response format ofthe tag

圖2 閱讀器結構圖

Fig.2 Structural diagram of the reader

閱讀器的工作原理是:標簽接收到閱讀器的響應幀后,將NRZ碼編碼成Manchester碼,并調制上載波后發送出去,閱讀器的高頻接口將該信息解調,即將載波信號濾除后,輸出Manchester碼到譯碼模塊;譯碼模塊將譯碼得到的NRZ碼串行輸出到通用異步收發器UART的接收模塊;接收模塊將其轉化為并行數據,送人并行CRC(cyclic redundancy check)模塊,UART發送模塊等待數據幀發送命令XMIT_CMD,當CRC模塊檢查到接收的數據正確,便將XMIT_CMD置為“1” ,發送模塊開始發送數據。

2 閱讀器設計方案

對目標芯片EP1 C6Q240C8,采用Quartus II開發軟件,使用VHDL語言完成對閱讀器各模塊的描述,并且調用第三方仿真工具ModelSim來進行時序仿真。Quartus II是Ahera公司的綜合性PLD開發軟件,支持原理圖、VHDL、Verilog—HDL等多種設計輸入形式,內嵌自有的綜合器以及仿真器,還可以調用第三方仿真工具完成從設計輸人到硬件配置的完整PLD設計流程。Quaaus II的設計步驟為設計輸入、設計編譯、功能仿真、時序仿真、硬件配置。

2.1 譯碼模塊

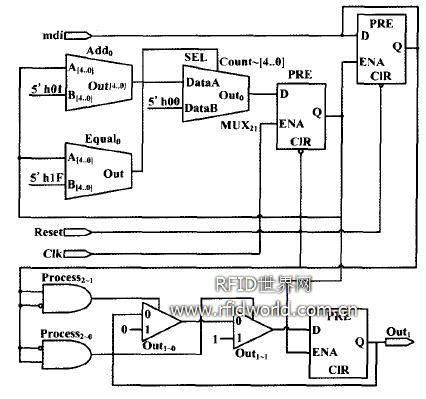

從電子標簽到閱讀器的數據傳輸可采用Manehester編碼,這將有利于發現傳輸中的錯誤。因為在比特長度內,“沒有變化”的狀態是不允許的。當多個標簽同時發送的數據位有不同值時,接收的上升沿和下降沿互相抵消,由于該狀態是不允許的,所以閱讀器利用該錯誤就可以判定碰撞發生的具體位置。在曼徹斯特編碼中,某比特位的值是由該比特長度內半個比特周期時的電平的變化(上升/下降)來表示的,從“1”跳變到“0”表示二進制“1”,從“0”跳變到“1”表示二進制“0”。

閱讀器的工作頻率為915 MHz,Manchester碼的傳送頻率為915 MHz/16。其基本設計原理是采用915 MHz作為基準時鐘clk ,利用分頻器得到基準時鐘的16分頻(clk/16)和8分頻(clk/8)。用2個D觸發器構成移位寄存器,輸人時鐘為(clk/8),將輸入的Manchester碼并行移出,并行移出的2個值為q1和q0。再構造一個比較器,采用clk/16作為輸入時鐘,這樣就能將Manchester碼在一個比特長度內的兩個電平值進行比較,如果q0=“1”,q1 =“0”,就輸出二進制“1”;如果qo=“0”,q1=“1”,就輸出二進制“0”。這樣就實現了Manchester碼的譯碼。

采用QuartusⅡ開發軟件,可以觀察到設計的RTL視圖,如圖3所示。其中mdi為輸入的Manchester碼,Out。為輸出的譯碼。

圖3 譯碼模塊的RTL視圖

Fig.3 RTL view of the decode block

表2 占用芯片資源情況表

Tab.2 The used chip resources

圖4 譯碼仿真波形

Fig.4 Decod e simulation wavcform

1001”;Out1為得到的八位二進制譯碼“11011010”。輸出的譯碼比輸入的Manchester碼延時一個周期。譯出八位二進制碼的時間僅為156.264 ns。因此,本設計能達到快速準確譯碼的目的,且占用資源少。

2.2 通用異步收發器接收模塊

接收器模塊接收譯碼模塊輸出的串行二進制碼。

并將其轉化為并行數據輸出。接收狀態機共有R_START(等待起始位)、R_CENTER(求中點)、R_WAIT(等待采樣)、R_SAMPLE(采樣)和R_STOP(停止)這5個狀態,如圖5所示。

圖5 UART接收器的接收狀態機

Fig.5 Receiving status principle of UART

2.3 并行CRC模塊

通常,CRC采用線性反饋移位寄存器的串行實現,本文采用一種并行CRC運算方法。CRC校驗碼采用多項式:x16 + x12 + x5 +1。使用16個移位寄存器,每次輸入8 bits數據,相當于一次并行運算就得到了串行移位運算時需要8次移位得到的結果,具有更高的處理速度,縮短了閱讀器對卡的響應時間。

2.4 通用異步收發器發送模塊

當發送模塊處于X_START狀態時,發送一個位時間寬度的邏輯0至輸出TXD ,緊接著狀態機轉入X_WAIT狀態。XCNT16是balk的計數器。X_WAIT狀態和接收狀態機中的R_WAIT狀態相似。計數器記到15時,轉入X_SHIFT狀態,實現待發數據的并串轉換,轉換完成回到X_WAIT狀態。當數據幀發送完畢,狀態機進入X_STOP狀態,等待另一個數據幀的發送命令。

3 下載配置

EP1C6Q240C8芯片支持被動串行和JTAG兩種下載模式 ,這里采用JTAG模式對芯片進行配置。下載電纜與電路板相連的是10針插座,采用1O個小方格來表示,配置電路如圖6所示(其中nCE0懸空,DA-TA。和DCLK使用高電平或低電平驅動)。

圖6 配置電路圖

Fig.6 Circuit diagram of configuration

FPGA是簡化SoC設計的一種新選擇,省略了單片機的許多附件部分。本文實現了基于ISO/IEC18000-6標準閱讀器的解碼、處理和發送功能。通過實驗證明,本設計具有解碼速度快、接收數據準確、識別率高等優點。

登錄

登錄

注冊

注冊